48V-to-PoL Isolated DC-DC Converters

The MAIN and SATELLITE Power Stamp are isolated DC-DC converters that converts a 48 V or 54 V bus voltage into a low voltage suitable for typical server's motherboard subsystems.

# **Key Features and Benefits**

- Over 93% peak efficiency at 1.8 Vout

- Over 91% peak efficiency at 1.0 Vout

- Up to 140 W continuous output power / 200 W peak

- Up to 70 A continuous output current / 100 A peak

- Wide 40 V to 60 V input voltage range

- Power density exceeding 300 W/in<sup>3</sup>

Parallelable with automatic phase shedding

- Source and sink mode for fast transient response

- Isolated power train

- Secondary side fully digital control

- Power Management Bus with configurable AVSBus® or Intel® SVID interface

- Industry standard SMT package

- · Reference designs for selected applications

## **Applications**

- Direct conversion from 48 V or 54 V bus

- High performance computing

- Servers, storage and data processing equipment

- Communication systems

- Intel® VR13.HC CPUs

- DDR4 memory

- IBM® POWER9™ CPUs

- Low voltage, high current ASICs and FPGAs

## 1. MODEL SELECTION

| PART NUMBER            | INPUT<br>VOLTAGE<br>[V] | OUTPUT<br>VOLTAGE*<br>[V] | OUTPUT<br>CURRENT<br>[A] | OUTPUT<br>CURRENT<br>[A peak] | EFFICIENCY<br>(Typical)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-------------------------|---------------------------|--------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAIN Power Stamps      |                         |                           |                          |                               | - Aller - Alle |

| ST4-1V8M07xx           | 40 – 60                 | 1.6 - 2.0                 | 70                       | 100                           | 93%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ST4-1V2M07xx           | 40 – 60                 | 1.16 – 1.26               | 70                       | 100                           | 92%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ST4-1V0M07xx           | 40 – 60                 | 0.5 – 1.1                 | 70                       | 100                           | 91%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SATELLITE Power Stamps |                         |                           |                          |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ST4-1V8S07xx           | 40 – 60                 | 1.6 – 2.0                 | 70                       | 100                           | 93%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ST4-1V2S07xx           | 40 – 60                 | 1.16 – 1.26               | 70                       | 100                           | 92%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ST4-1V0S07xx           | 40 – 60                 | 0.5 – 1.1                 | 70                       | 100                           | 91%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Controller IC          |                         |                           |                          |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| STPSA60                | -                       | -                         | -                        | -/-                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

<sup>\*</sup> NOTE: Output voltage range of typical applications - Contact factory for NVM configuration files for different output voltage settings.

## 2. ORDER INFORMATION

| PRODUCT<br>FAMILY<br>ST       | INPUT<br>VOLTAGE | - | OUTPUT<br>VOLTAGE<br>1V8                  | MODULE STYLE              | OUTPUT<br>CURRENT | OPTIONS                                                                                       |

|-------------------------------|------------------|---|-------------------------------------------|---------------------------|-------------------|-----------------------------------------------------------------------------------------------|

| Power<br>Stamp form<br>factor | 4 = 40 - 60 V    | - | 1V8 = 1.8 V<br>1V2 = 1.2 V<br>1V0 = 1.0 V | M = MAIN<br>S = SATELLITE | 07 = 70 A         | mn = custom (m = letter, n = digit) G = Tray pkg. Ex = Eval. Bd. (x = Eval. Bd. model number) |

<sup>\*</sup> NOTE: Preferred parts

## 3. EVALUATION BOARDS

| ARCHITECTURE | FAMILY  | RELEASE DATE | TDP         | SOCKET                         | MODULE TYPE (number of modules)   | PART NUMBER   |

|--------------|---------|--------------|-------------|--------------------------------|-----------------------------------|---------------|

| Skylake      | Xeon®   | Q3/2017      | 140 – 205 W | Socket P                       | SATELLITE (3) + STPSA60           | ST4-1V8S07E1  |

| Cascade Lake | Xeon®   | 2018         | 165 – 205 W | Socket P                       | SATELLITE (3) + STPSA60           | ST4-1V8S07E1  |

| Ice Lake     | Xeon®   | 2018 / 2019  | Up to 230 W | Socket P+                      | MAIN / STPSA60 +<br>SATELLITE (3) | ST4-1V8M07E2  |

| ASICs        | -       | H1/2019      | Up to 600W  | Mini Slammer /<br>Load Slammer | MAIN + SATELLITE (5)              | ST4-1VxM07E3* |

| LaGrange     | POWER9™ | H2/2019      | -           | FC-PLGA                        | -                                 | ST4-1V0M07E4  |

<sup>\*</sup> **NOTE:** x = Output voltage of installed Power Stamp module.

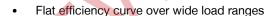

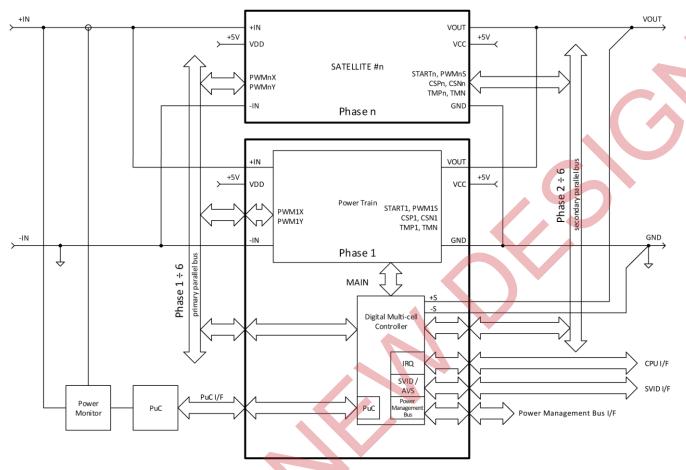

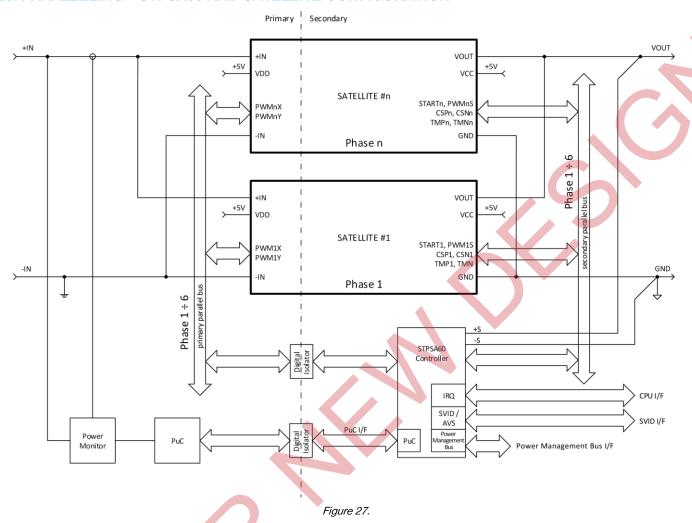

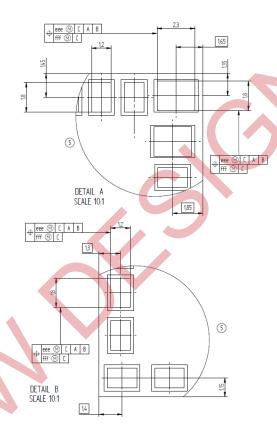

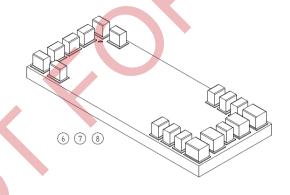

## 4. TYPICAL SERVER MOTHERBOARD APPLICATION

Figure 1. Typical server motherboard application

## 5. ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which damage to the device may occur. These are stress ratings only and functional operation of the device at these conditions is not implied. Operating outside maximum recommended conditions for extended periods may affect product reliability and result in device failures.

| SYMBOL         | PARAMETER                             |   | MIN  | MAX  | UNITS |

|----------------|---------------------------------------|---|------|------|-------|

| +IN to -IN     | Non-operating continuous input voltag | e | -0.3 | 76   | V     |

| Vout to GND    | Continuous output voltage             |   | -0.3 | TBC  | V     |

| VDD            | Primary auxiliary bias voltage        |   | -0.3 | 14   | V     |

| VCC            | Secondary auxiliary bias voltage      |   | -0.3 | 7    | V     |

| PWM_X, PWM_Y   | (2)                                   |   | -0.3 | 6.65 | V     |

| PWM_S, START   | (3)                                   |   | -0.3 | 7    | V     |

| START          | (3)                                   |   | -0.3 | 7    | V     |

| TMN, TMP       | (3)                                   |   | -0.3 | 7    | V     |

| CSP, CSN       | (3) (4)                               |   | -0.3 | 2.5  | V     |

| CSP, CSN       | (3) (4)                               |   | -0.3 | 2.5  | V     |

| All other pins | (3)                                   |   | -0.3 | 7    | V     |

| Tmax           | Ambient temperature                   |   | -40  | +85  | °C    |

| Tstg           | Storage temperature                   |   | -40  | +100 | °C    |

| Wind           | (5)                                   |   | 200  | -    | LFM   |

Notes:

- 1) All voltages referenced to GND unless otherwise specified

- 2) Need to be lower than VDD under any condition

- 3) Need to be lower than VCC under any condition

- 4) Max differential voltage to be limited within 100mV

- 5) Fans must be used for cooling when working

## 6. SPECIFICATIONS

Specifications are typical and apply for the conditions: VDD = 5 V, VCC = 5 V, Tamb = 25°C unless otherwise noted.

# 7. INPUT SPECIFICATIONS - ALL MODELS

| PARAMETER                                                                                                                                | SYMBOL                | MIN | TYP | MAX | UNITS             |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|-------------------|

| Input voltage Continuous; VDD, VCC applied                                                                                               | V <sub>IN</sub>       | 40  | 48  | 60  | V                 |

| Maximum input current $V_{IN} = 40 \text{ V} - 60 \text{ V}, \text{ I}_{O} = \text{I}_{O\_max}$                                          | I <sub>IN_max</sub>   | -   | -   | 4   | Α                 |

| Input quiescent current $V_{IN} = 48 \text{ V}, I_O = 0 \text{ A}, \text{ enabled}$                                                      | I <sub>IN_NL</sub>    |     | TBC |     | mA                |

| Input stand by current $V_{IN} = 48 \text{ V}$ , disabled                                                                                | I <sub>IN_stdby</sub> |     | TBC |     | mA                |

| Inrush transient                                                                                                                         | I <sup>2</sup> t      |     |     |     | $A^2s$            |

| Input reflected ripple current 5 Hz to 20 MHz, $1\mu$ H source impedance; $V_{IN} = 40 \text{ V}$ to $60 \text{ V}$ , $I_0 = I_{0\_max}$ | l <sub>IN_rr</sub>    |     | TBC |     | mA <sub>p-p</sub> |

| Input ripple rejection                                                                                                                   | PSRR                  |     | TBC |     | dB                |

| Internal input capacitance                                                                                                               | $C_{IN}$              |     | TBC |     | μF                |

## 8. OUTPUT SPECIFICATIONS\* - 1.8 V

| PARAMETER                                                                                                                                                                                                 | SYMBOL                | MIN   | TYP            | MAX            | UNITS                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|----------------|----------------|------------------------|

| Output voltage setpoint                                                                                                                                                                                   | V <sub>OUT</sub>      | 1.820 | 1.83           | 1.839          | V                      |

| Output voltage trim range                                                                                                                                                                                 | $V_{\text{OUT\_adj}}$ | 1.6   |                | 2.0            | V                      |

| Trim VID resolution                                                                                                                                                                                       |                       |       | 10             |                | mV                     |

| Output Regulation  Line (V <sub>IN</sub> = V <sub>IN_min</sub> to V <sub>IN_max</sub> )  Load (lout = loutmin to loutmax)  Temperature (T <sub>ref</sub> = T <sub>amb_min</sub> to T <sub>amb_max</sub> ) |                       |       | -<br>-<br>-    | 8<br>10<br>TBC | mV<br>mV<br>%Vout_nom  |

| Total regulation band AC, lout = lout_min to lout_max                                                                                                                                                     |                       |       | -              | 44             | $mV_{p-p}$             |

| Output voltage ripple and noise  V <sub>IN</sub> = 48 V and I <sub>OUT</sub> = I <sub>OUT_min</sub> to I <sub>OUT_max</sub> 5 Hz to 20 MHz bandwidth, nominal output capacitance                          | $V_{r}$               |       | -              | 20             | $mV_{p-p}$             |

| Output capacitance<br>ESR > 0.15 m $\Omega$<br>ESR > 10 m $\Omega$                                                                                                                                        | C <sub>OUT</sub>      |       | <del>-</del> , | TBC<br>TBC     | μF                     |

| Continuous output current in either source or sink mode                                                                                                                                                   | Іоит                  | 0     |                | 70             | А                      |

| Peak output current TBC, in either source or sink mode                                                                                                                                                    | I <sub>OUT_peak</sub> |       | -              | 100            | A <sub>peak</sub>      |

| Output current limit<br>TBC                                                                                                                                                                               | lout_cl               |       | 150            | 180            | % I <sub>OUT_max</sub> |

| Output short circuit current TBC                                                                                                                                                                          | lout_sc               |       |                | TBC            | ARMS                   |

| Efficiency $V_{IN} = 48 \text{ V}, T_{amb} = 25^{\circ}\text{C}$ $I_{OUT} = 50\% \text{ of } I_{OUT\_max}, V_{OUT} = V_{OUT\_nom}$                                                                        | η                     | 92    | 93             |                | %                      |

| Switching frequency                                                                                                                                                                                       | f <sub>sw</sub>       | 200   | 450            | 600            | kHz                    |

<sup>\*</sup> NOTE: Contact factory for NVM configuration files for different output voltage settings

# 9. OUTPUT SPECIFICATIONS\* - 1.2 V

| PARAMETER                                                                                                                                                                                     | SYMBOL                | MIN   | TYP         | MAX           | UNITS                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------------|---------------|------------------------|

| Output voltage setpoint                                                                                                                                                                       | $V_{OUT}$             | 1.194 | 1.2         | 1.206         | V                      |

| Output voltage trim range                                                                                                                                                                     | $V_{OUT\_adj}$        | 1.16  |             | 1.26          | V                      |

| Trim VID resolution                                                                                                                                                                           |                       |       | 5           |               | mV                     |

| Output Regulation  Line $(V_{IN} = V_{IN\_min} \text{ to } V_{IN\_max})$ Load $(I_{OUT} = I_{OUTmin} \text{ to } I_{OUTmax})$ Temperature $(T_{ref} = T_{amb\_min} \text{ to } T_{amb\_max})$ |                       |       | -<br>-<br>- | 2<br>8<br>TBC | mV<br>mV<br>%VouT_nom  |

| Total regulation band AC, Ιουτ = Ιουτ_min to Ιουτ_max                                                                                                                                         |                       |       | -           | -             | $mV_{p-p}$             |

| Output voltage ripple and noise  V <sub>IN</sub> = 48 V and lour = lour_min to lour_max  5 Hz to 20 MHz bandwidth, nominal output capacitance                                                 | $V_{r}$               |       | - (         | 12            | $mV_{p-p}$             |

| Output capacitance<br>ESR > 0.15 m $\Omega$<br>ESR > 10 m $\Omega$                                                                                                                            | $C_OUT$               |       | <u>/-</u> , | TBC<br>TBC    | μF                     |

| Continuous output current in either source or sink mode                                                                                                                                       | louт                  | 0     |             | 70            | А                      |

| Peak output current TBC, in either source or sink mode                                                                                                                                        | I <sub>OUT_peak</sub> |       |             | 100           | A <sub>peak</sub>      |

| Output current limit TBC                                                                                                                                                                      | lout_cl               |       | 150         | 180           | % I <sub>OUT_max</sub> |

| Output short circuit current<br>TBC                                                                                                                                                           | lout_sc               |       |             | TBC           | ARMS                   |

| Efficiency $V_{IN} = 48 \text{ V}, T_{amb} = 25 ^{\circ}\text{C}$ $I_{OUT} = 50\% \text{ of } I_{OUT\_max}, V_{OUT} = V_{OUT\_nom}$                                                           | η                     | 91    | 92          |               | %                      |

| Switching frequency                                                                                                                                                                           | f <sub>SW</sub>       | 200   | 450         | 600           | kHz                    |

<sup>\*</sup> NOTE: Contact factory for NVM configuration files for different output voltage settings

## 10. OUTPUT SPECIFICATIONS\* - 1.0 V

| PARAMETER                                                                                                                                                                        | SYMBOL                | MIN   | TYP         | MAX               | UNITS                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------------|-------------------|-----------------------------------|

| Output voltage setpoint                                                                                                                                                          | $V_{OUT}$             | 0.995 | 1.0         | 1.005             | V                                 |

| Output voltage trim range                                                                                                                                                        | $V_{OUT\_adj}$        | 0.8   |             | 1.1               | V                                 |

| Trim VID resolution                                                                                                                                                              |                       |       | 5           |                   | mV                                |

| Output Regulation Line ( $V_{IN} = V_{IN\_min}$ to $V_{IN\_max}$ ) Load ( $I_{OUT} = I_{OUTmin}$ to $I_{OUTmax}$ ) Temperature ( $T_{ref} = T_{amb\_min}$ to $T_{amb\_max}$ )    |                       |       | -<br>-<br>- | TBC<br>TBC<br>TBC | mV<br>mV<br>%V <sub>OUT_nom</sub> |

| Total regulation band AC, louт= lout_min to lout_max                                                                                                                             |                       |       | 180         |                   | $mV_{p-p}$                        |

| Output voltage ripple and noise  V <sub>IN</sub> = 48 V and I <sub>OUT</sub> = I <sub>OUT_min</sub> to I <sub>OUT_max</sub> 5 Hz to 20 MHz bandwidth, nominal output capacitance | $V_{r}$               |       | <u>.</u>    | TBC               | $mV_{p-p}$                        |

| Output capacitance<br>ESR > 0.15 m $\Omega$<br>ESR > 10 m $\Omega$                                                                                                               | Соит                  |       | <b>\.</b> / | TBC<br>TBC        | μF                                |

| Continuous output current in either source or sink mode                                                                                                                          | Іоит                  | 0     |             | 70                | Α                                 |

| Peak output current TBC, in either source or sink mode                                                                                                                           | I <sub>OUT_peak</sub> |       | -           | 100               | A <sub>peak</sub>                 |

| Output current limit<br>TBC                                                                                                                                                      | lout_ct               |       | 150         | 180               | % I <sub>OUT_max</sub>            |

| Output short circuit current<br>TBC                                                                                                                                              | lout_sc               |       |             | TBC               | A <sub>RMS</sub>                  |

| Efficiency $V_{IN} = 48 \text{ V}, T_{amb} = 25^{\circ}\text{C}$ $I_{OUT} = 50\% \text{ of } I_{OUT\_max}, V_{OUT} = V_{OUT\_nom}$                                               | η                     | 90    | 91          |                   | %                                 |

| Switching frequency                                                                                                                                                              | f <sub>sw</sub>       | 200   | 450         | 600               | kHz                               |

<sup>\*</sup> NOTE: Contact factory for NVM configuration files for different output voltage settings

# 11. FEATURE SPECIFICATIONS

| PIN OR PAD                           | PARAMETER                                                                | MIN   | TYP   | MAX  | UNITS              |

|--------------------------------------|--------------------------------------------------------------------------|-------|-------|------|--------------------|

| Supply Pins                          |                                                                          |       | _     |      |                    |

| VDD                                  | VDD supply voltage                                                       | 4.5   | 5     | 5.5  | V                  |

|                                      | VDD supply current                                                       | 4.5   | 25    | 50   | mA <sub>PEAK</sub> |

| VCC                                  | VCC supply voltage                                                       | 4.5   | 5     | 5.5  | V                  |

| VDEO                                 | VCC supply current                                                       |       | 50    | 100  | mA <sub>PEAK</sub> |

| VREG                                 | Not used                                                                 |       | -     |      |                    |

| VCTRL                                | Not used                                                                 | _     | -     |      |                    |

| Under Voltage Lock Out               |                                                                          |       | 4.0   | 10   | 2/                 |

| VDD                                  | VDD rising threshold                                                     |       | 4.2   | 4.3  | V                  |

| 0 1 15 11                            | Hysteresis                                                               | _     |       | 500  | mV                 |

| Output Enable                        | Innut HCH violen                                                         |       |       | 0.7  | ma\/               |

|                                      | Input HIGH, rising                                                       | 0.4   |       | 0.7  | mV                 |

|                                      | Input LOW, falling                                                       | 0.4   |       |      | mV                 |

| 0 1 1                                | Leakage, V <sub>EN</sub> = 1.1V                                          |       |       | 1    | μΑ                 |

| Protections                          |                                                                          |       | 700   |      |                    |

| +S                                   | Feedback disconnection                                                   |       | 700   |      | mV                 |

| -S                                   | Feedback disconnection                                                   |       | 500   |      | mV                 |

| VSRMON                               | Peak protection                                                          |       | 3.045 |      | V                  |

| Power Management Bus                 |                                                                          |       |       |      |                    |

| SDA                                  | Input HIGH, rising                                                       | 1.8   |       |      | V                  |

| SCL                                  | Input LOW, falling                                                       |       |       | 1.4  | V                  |

| SDA<br>SALERT                        | Output pull down, I <sub>SINK</sub> = 5 mA                               |       |       | 13   | Ω                  |

| SADDR                                | R <sub>DOWN</sub> resistor<br>(see Power Management Bus Address section) |       | 10    |      | kΩ                 |

| SVID / AVS Interface                 |                                                                          |       |       |      |                    |

| SVDAT / AVSMDAT                      | Input HIGH, rising                                                       | 0.65  |       |      | V                  |

| SVCLK / AVSCLK                       | Input LOW, falling                                                       |       |       | 0.45 | V                  |

| SVDAT / AVSMDAT<br>SV_ALRT / AVSSDAT | Output pull down, Isink = 5 mA                                           |       |       | 13   | Ω                  |

| CPU Link Interface                   |                                                                          |       |       |      |                    |

| VR_HOT#                              |                                                                          |       |       | 13   | Ω                  |

| VR_RDY                               | Output pull down, Isink = 5 mA                                           |       |       | 13   | Ω                  |

| FAULT#                               |                                                                          |       |       | 45   | Ω                  |

| VCCIO_OK                             | Input HIGH, ri <mark>si</mark> ng                                        | 1.7   |       |      | V                  |

| 10010_010                            | Input LOW, falling                                                       |       |       | 1.5  | V                  |

| PFAULT_IN#                           | Pull up current                                                          |       | 10    |      | μA                 |

| PIN_ALERT#                           | Output pull down, I <sub>SINK</sub> = 5 mA                               |       |       | 13   | Ω                  |

| Primary uController Inte             | rface                                                                    |       |       |      |                    |

| PUCCS, PUCCK                         | Input HIGH, rising                                                       | 1.7   |       |      | V                  |

| PUCDTI                               | Input LOW, falling                                                       |       |       | 1.5  | V                  |

| PUCDTO                               | Output HIGH voltage, Isource = 1 mA                                      | 4.5V  |       |      |                    |

| ТООБТО                               | Output LOW voltage, Isink = 5 mA                                         |       | 125   | 250  | mV                 |

| Output P <mark>i</mark> ns           |                                                                          |       |       |      |                    |

| PWMx                                 | Output HIGH voltage, Isource = 1 mA                                      | 4.90  | 4.95  |      | V                  |

| STARTx                               | Output LOW voltage, Isink = 1 mA                                         |       | 25    | 50   | mV                 |

| STARTx                               | Active high impedance (HiZ)                                              | 1.55. | 1.60  | 1.65 | V                  |

## 12. GENERAL SPECIFICATIONS

| PARAMETER                                                                                                                                                                                                  | SYMBOL | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|-------|

| Relative humidity Operating, non-condensing                                                                                                                                                                | RH     | 10   |      | 90   | %     |

| Altitude                                                                                                                                                                                                   |        | -500 |      | 4000 | ft.   |

| Calculated MTBF Calculated Per Telcordia SR-332, Issue2, Method 1, Case 3 V <sub>IN</sub> = 48 V, V <sub>OUT</sub> = 1.83 V, I <sub>OUT</sub> = 70 A, T <sub>amb</sub> = 40°C, FIT = 10 <sup>9</sup> /MTBF | MTBF   |      | TBC  |      | Hours |

| Weight                                                                                                                                                                                                     |        |      | 12   |      | g     |

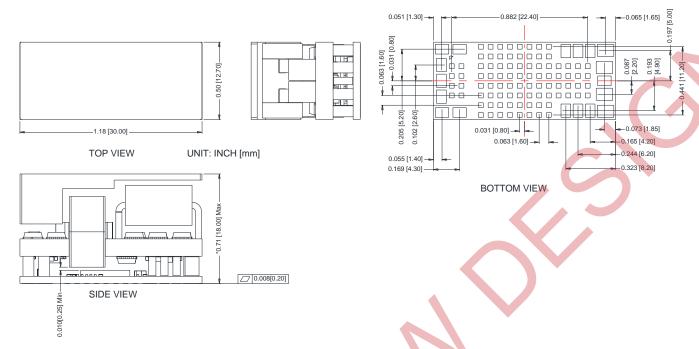

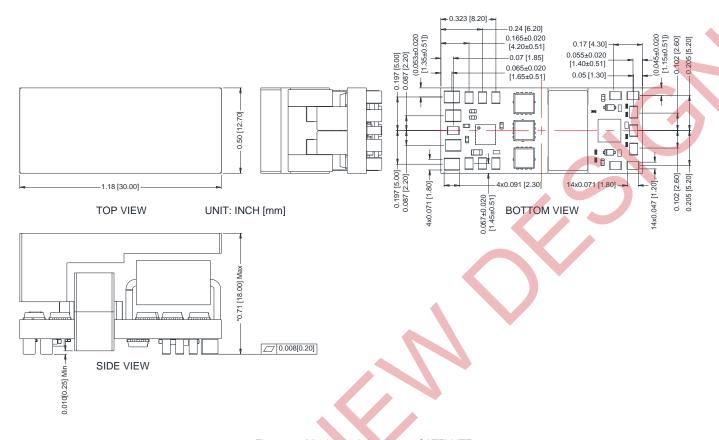

| Dimensions (L x W x H)                                                                                                                                                                                     |        | 30   | 12.7 | 18   | mm    |

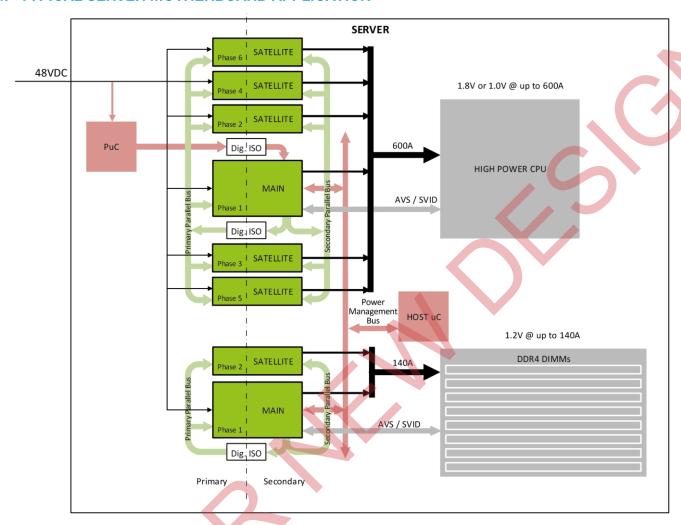

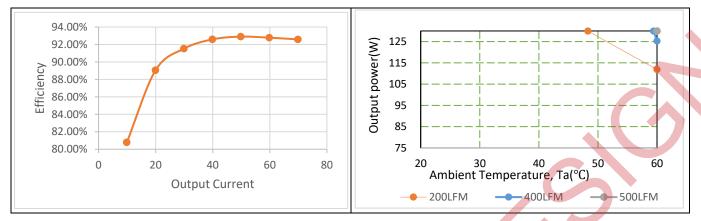

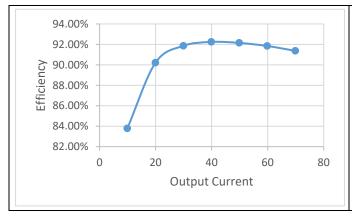

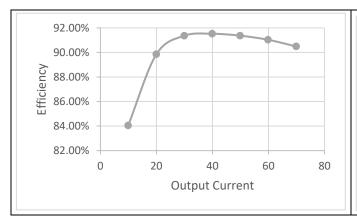

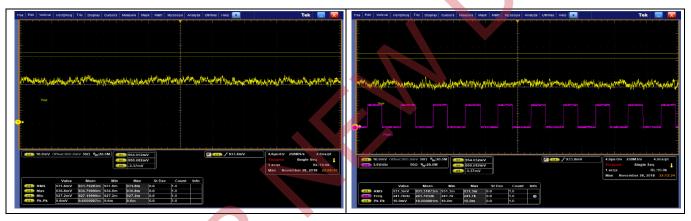

## 13. PERFORMANCE CHARACTERISTICS - 1.8 V

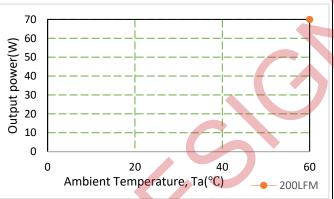

Figure 2. Efficiency and Power Dissipation

Figure 3. Thermal Derating Curves, Vin=48V

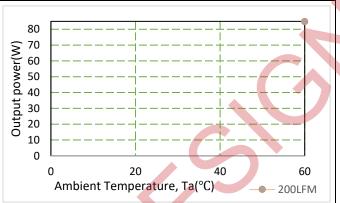

Figure 4. Ripple and Noise

Figure 5. Switching Frequency vs. Output Current

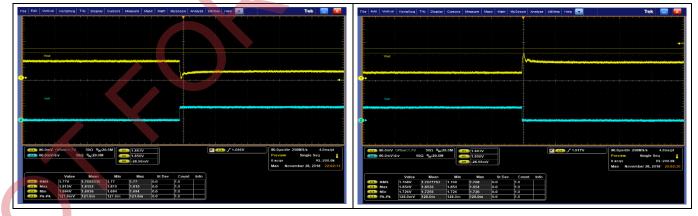

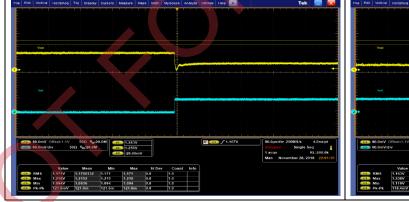

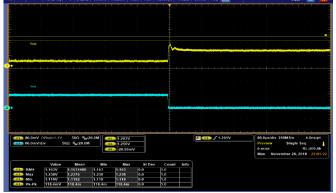

Figure 6. Transient Response – 10% Iout to 100% Iout, VIN = 48 V

Figure 7. Transient Response – 100%  $I_{OUT}$  to 10%  $I_{OUT}$ ,  $V_{IN}$  = 48 V

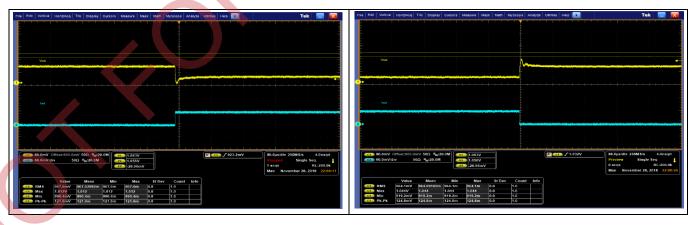

## 14. PERFORMANCE CHARACTERISTICS - 1.2 V

Figure 8. Efficiency and Power Dissipation

Figure 9. Thermal Derating Curves

Figure 10. Ripple and Noise

Figure 11. Switching Frequency vs. Output Current

Figure 12. Transient Response – 10% Iout to 100% Iout, VIN = 48 V

Figure 13. Transient Response – 100%  $I_{OUT}$  to 10%  $I_{OUT}$ ,  $V_{IN}$  = 48 V

**Asia-Pacific** +86 755 298 85888 **Europe, Middle East** +353 61 49 8941

## 15. PERFORMANCE CHARACTERISTICS - 1.0 V

Figure 14. Efficiency and Power Dissipation

Figure 15. Thermal Derating Curves

Figure 16. Ripple and Noise

Figure 17. Switching Frequency vs. Output Current

Figure 18. Transient Response – 10% Iout to 100% Iout, VIN = 48 V

Figure 19. Transient Response – 100% Iout to 10% Iout, VIN = 48 V

www.powerstamp.org

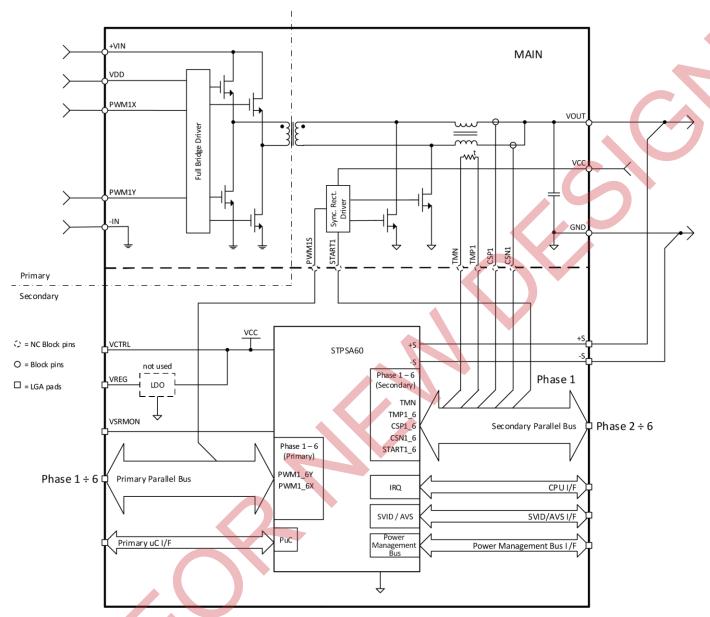

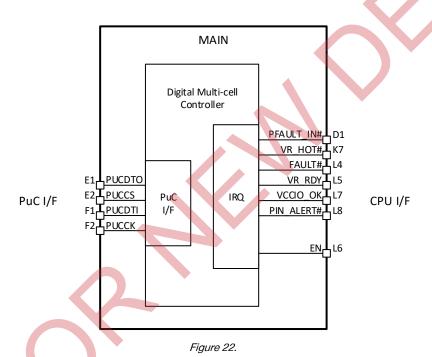

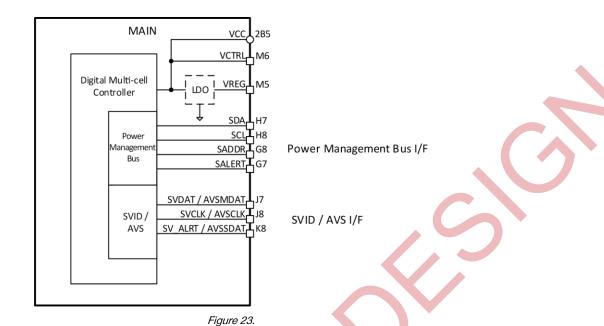

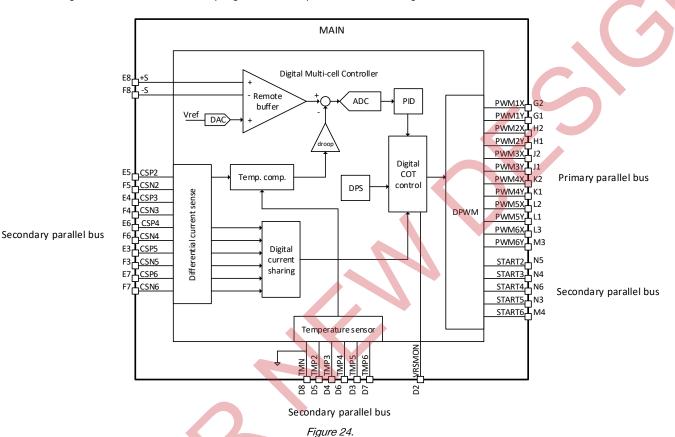

## 16. BLOCK DIAGRAM - MAIN

Figure 20.

**Asia-Pacific** +86 755 298 85888 Europe, Middle East +353 61 49 8941

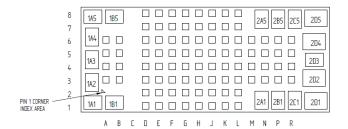

## 17. PACKAGE PINOUT - MAIN

| INPUT |          |  |  |  |

|-------|----------|--|--|--|

| PAD # | FUNCTION |  |  |  |

| 1A1   | +IN      |  |  |  |

| 1A2   | PWM_Y    |  |  |  |

| 1A3   | VDD      |  |  |  |

| 1A4   | PWM_X    |  |  |  |

| 1A5   | +IN      |  |  |  |

| 1B1   | -IN      |  |  |  |

| 1B5   | -IN      |  |  |  |

|       |          |  |  |  |

|       |          |  |  |  |

|       |          |  |  |  |

|       |          |  |  |  |

| OUTPUT |          |  |  |  |

|--------|----------|--|--|--|

| PAD #  | FUNCTION |  |  |  |

| 2A1    | START    |  |  |  |

| 2A5    | PWM_S    |  |  |  |

| 2B1    | TMN      |  |  |  |

| 2B5    | VCC      |  |  |  |

| 201    | TMP      |  |  |  |

| 205    | ESP /    |  |  |  |

| 201    | GND      |  |  |  |

| 202    | VOUT     |  |  |  |

| 203    | ESN      |  |  |  |

| 204    | VOUT     |  |  |  |

| 205    | GND      |  |  |  |

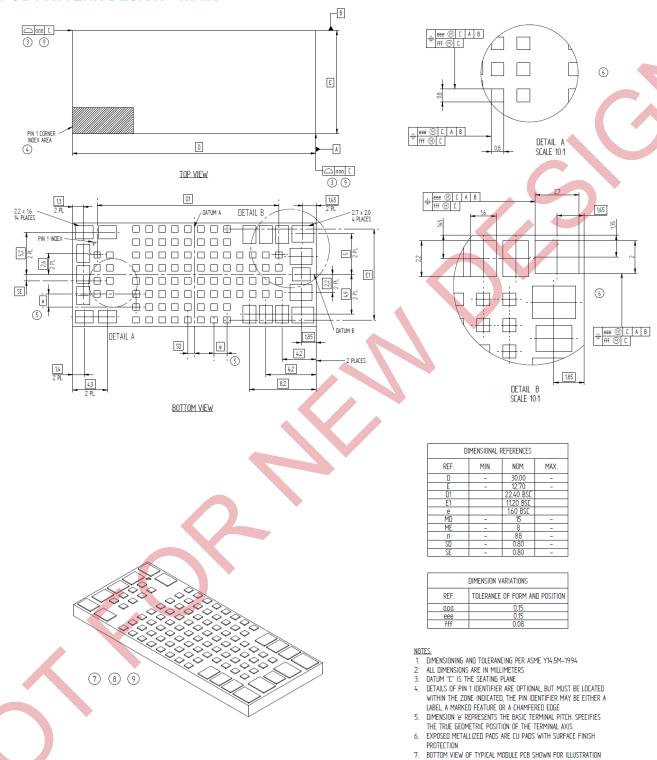

### TOP VIEW THROUGH THE PRODUCT

|   | LAND GRID ARRAY PAD DESIGNATION |     |     |            |        |        |        |       |                    |                      |            |        |        |     |     |

|---|---------------------------------|-----|-----|------------|--------|--------|--------|-------|--------------------|----------------------|------------|--------|--------|-----|-----|

|   | A                               | В   | С   | D          | E      | F      | G      | Н     | J                  | K                    | L          | М      | N      | Р   | R   |

| 1 | N/A                             | N/A | N/A | PFAULT_IN# | PUEDTO | PUCOTI | PWM1Y  | PWM2Y | PWM3Y              | PWM4Y                | PWM5Y      | N/A    | N/A    | N/A | N/A |

| 2 | N/A                             | N/A | N/A | VSRMON     | PUCCS  | PUCCK  | PWM1X  | PWM2X | PWM3X              | PWM4X                | PWM5X      | N/A    | N/A    | N/A | N/A |

| 3 | -IN                             | -IN | N/A | TMP5       | CSP5   | ESN5   | GND    | GND   | GND                | GND                  | PWM6X      | PWM6Y  | START5 | GND | GND |

| 4 | -IN                             | -IN | N/A | TMP3       | ESP3   | ESN3   | GND    | GND   | GND                | GND                  | FAULT#     | START6 | START3 | GND | GND |

| 5 | -IN                             | -IN | N/A | TMP2       | CSP2   | CSN2   | GND    | GND   | GND                | GND                  | VR_RDY     | VREG   | START2 | GND | GND |

| 6 | -IN                             | -IN | N/A | TMP4       | ESP4   | ESN4   | GND    | GND   | GND                | GND                  | EN         | VETRL  | START4 | GND | GND |

| 7 | N/A                             | N/A | N/A | TMP6       | ESP6   | ESN6   | SALERT | SDA   | SVDAT /<br>AVSMDAT | VR_HOT#              | VCCIO_OK   | N/A    | N/A    | N/A | N/A |

| 8 | N/A                             | N/A | N/A | TMN        | +\$    | -S     | SADDR  | SCL   | SVELK /<br>AVSELK  | SV_ALRT /<br>AVSSDAT | PAD_ALERT# | N/A    | N/A    | N/A | N/A |

Land designator per JEP95, SEC. 3, SPP-010 AND SPP-020, Zero orientation with pin 1 in lower left corner

## 18. PIN DESCRIPTION - MAIN

| PAD# | PAD NAME   | PAD FUNCTION NOTE                                       |

|------|------------|---------------------------------------------------------|

| A1   | N/A        | No Pad present                                          |

| B1   | N/A        | No Pad present                                          |

| C1   | N/A        | No Pad present                                          |

| D1   | PFAULT_IN# | Primary side fault indicator                            |

| E1   | PUCDTO     | Primary side uC data output                             |

| F1   | PUCDTI     | Primary side uC data input                              |

| G1   | PWM1Y      | PWM signal for Satellite 1                              |

| H1   | PWM2Y      | PWM signal for Satellite 2                              |

| J1   | PWM3Y      | PWM signal for Satellite 3                              |

| K1   | PWM4Y      | PWM signal for Satellite 4                              |

| L1   | PWM5Y      | PWM signal for Satellite 5                              |

| M1   | N/A        | No Pad present                                          |

| N1   | N/A        | No Pad present                                          |

| P1   | N/A        | No Pad present                                          |

| R1   | N/A        | No Pad present                                          |

| A2   | N/A        | No Pad present                                          |

| B2   | N/A        | No Pad present                                          |

| C2   | N/A        | No Pad present                                          |

| D2   | VSRMON     | Feed-forward sensor input Internal 10k pull-down to GND |

| E2   | PUCCS      | Primary side uC chip select                             |

| F2   | PUCCK      | Primary side u-controller clock                         |

| PAD #      | PAD NAME     | PAD FUNCTION                                | NOTE                                      |

|------------|--------------|---------------------------------------------|-------------------------------------------|

| G2         | PWM1X        | PWM signal for Satellite 1                  | 1012                                      |

| H2         | PWM2X        | PWM signal for Satellite 2                  |                                           |

| J2         | PWM3X        | PWM signal for Satellite 3                  |                                           |

| K2         | PWM4X        | PWM signal for Satellite 4                  |                                           |

| L2         | PWM5X        | PWM signal for Satellite 5                  |                                           |

| M2         | N/A          | No Pad present                              |                                           |

| N2         | N/A          | No Pad present                              |                                           |

| P2         | N/A          | No Pad present                              |                                           |

| R2         | N/A          | No Pad present                              |                                           |

| A3         | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| В3         | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| C3         | N/A          | No Pad present                              |                                           |

| D3         | TMP5         | Temperature sense Satellite 5               |                                           |

| E3         | CSP5         | Current sense +v Satellite 5                | Internal 1nF cap between CSP5 and CSN5    |

| F3         | CSN5         | Current sense -v Satellite 5                | Internal 1nF cap between CSP5 and CSN5    |

| G3         | GND          | Secondary side ground                       |                                           |

| Н3         | GND          | Secondary side ground                       |                                           |

| J3         | GND          | Secondary side ground                       |                                           |

| К3         | GND          | Secondary side ground                       |                                           |

| L3         | PWM6X        | PWM signal for Satellite 6                  |                                           |

| М3         | PWM6Y        | PWM signal for Satellite 6                  |                                           |

| N3         | START5       | Start for Satellite 5                       |                                           |

| P3         | GND          | Secondary side ground                       |                                           |

| R3         | GND          | Secondary side ground                       |                                           |

| A4         | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| B4         | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| C4         | N/A          | No Pad present                              |                                           |

| D4         | TMP3         | Temperature sense Satellite 3               | have all 16 F and hat was a CODO and CONO |

| E4         | CSP3<br>CSN3 | Current sense +v Satellite 3                | Internal InF cap between CSP3 and CSN3    |

| F4<br>G4   | GND          | Current sense -v Satellite 3                | Internal 1nF cap between CSP3 and CSN3    |

| H4         | GND          | Secondary side ground Secondary side ground |                                           |

| J4         | GND          | Secondary side ground                       |                                           |

| K4         | GND          | Secondary side ground                       |                                           |

| L4         | FAULT#       | Programmable fault indicator                |                                           |

| M4         | START6       | Start for Satellite 6                       |                                           |

| N4         | START3       | Start for Satellite 3                       |                                           |

| P4         | GND          | Secondary side ground                       |                                           |

| R4         | GND          | Secondary side ground                       |                                           |

| <b>A</b> 5 | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| B5         | N/C (-In)    | Pad present, N/C, Thermal via               |                                           |

| <b>C</b> 5 | N/A          | No Pad present                              |                                           |

| <b>D</b> 5 | TMP2         | Temperature sense Satellite 2               |                                           |

| <b>E</b> 5 | CSP2         | Current sense +v Satellite 2                | Internal 1nF cap between CSP2 and CSN2    |

| F5         | CSN2         | Current sense -v Satellite 2                | Internal 1nF cap between CSP2 and CSN2    |

| <b>G5</b>  | GND          | Secondary side ground                       |                                           |

| H5         | GND          | Secondary side ground                       |                                           |

| J5         | GND          | Secondary side ground                       |                                           |

| K5         | GND          | Secondary side ground                       |                                           |

| L5         | VR_RDY       | Voltage regulator ready signal              | TBC                                       |

| M5         | VREG         | Optional regulator input                    |                                           |

| N5         | START2       | Start for Satellite 3                       |                                           |

|            |              |                                             |                                           |

**Asia-Pacific** +86 755 298 85888 **Europe, Middle East** +353 61 49 8941

| PAD #      | PAD NAME            | PAD FUNCTION                                           | NOTE                                                                                                             |

|------------|---------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| P5         | GND                 | Secondary side ground                                  | 1012                                                                                                             |

| R5         | GND                 | Secondary side ground                                  |                                                                                                                  |

| A6         | N/C (-Vin)          | Pad present, N/C, Thermal via                          |                                                                                                                  |

| В6         | N/C (-Vin)          | Pad present, N/C, Thermal via                          |                                                                                                                  |

| C6         | N/A                 | No Pad present                                         |                                                                                                                  |

| D6         | TMP4                | Temperature sense Satellite 4                          |                                                                                                                  |

| <b>E</b> 6 | CSP4                | Current sense +v Satellite 4                           | Internal 1nF cap between CSP4 and CSN4                                                                           |

| F6         | CSN4                | Current sense -v Satellite 4                           | Internal 1nF cap between CSP4 and CSN4                                                                           |

| G6         | GND                 | Secondary side ground                                  |                                                                                                                  |

| Н6         | GND                 | Secondary side ground                                  |                                                                                                                  |

| J6         | GND                 | Secondary side ground                                  |                                                                                                                  |

| <b>K</b> 6 | GND                 | Secondary side ground                                  |                                                                                                                  |

| L6         | EN                  | Enable signal                                          | TBC                                                                                                              |

| М6         | VCTRL               | Controller supply voltage                              | Internal 10hm resistor between VCTRL pad and power supply of STPSA60 controller                                  |

| N6         | START4              | Start for Satellite 4                                  |                                                                                                                  |

| P6         | GND                 | Secondary side ground                                  |                                                                                                                  |

| R6         | GND                 | Secondary side ground                                  |                                                                                                                  |

| <b>A</b> 7 | N/A                 | No Pad present                                         |                                                                                                                  |

| B7         | N/A                 | No Pad present                                         |                                                                                                                  |

| <b>C</b> 7 | N/A                 | No Pad present                                         |                                                                                                                  |

| D7         | TMP6                | Temperature sense Satellite 6                          |                                                                                                                  |

| E7         | CSP6                | Current sense +v Satellite 6                           | Internal 1nF cap between CSP6 and CSN6                                                                           |

| F7         | CSN6                | Current sense -v Satellite 6                           | Internal 1nF cap between CSP6 and CSN6                                                                           |

| G7         | SALERT              | Power Management Bus Alert                             | TBC                                                                                                              |

| H7         | SDA                 | Power Management Bus data                              | TBC                                                                                                              |

| J7         | SVDAT / AVSMDAT     | SVID data_/ AVS MData                                  | TBC                                                                                                              |

| <b>K</b> 7 | VR_HOT#             | SVI VR hot                                             |                                                                                                                  |

| L7         | VCCIO_OK            | VCC fault shutdown – immediate unit shutdown           | TBC                                                                                                              |

| M7         | N/A                 | No Pad present                                         |                                                                                                                  |

| N7         | N/A                 | No Pad present                                         |                                                                                                                  |

| P7         | N/A                 | No Pad present                                         |                                                                                                                  |

| R7         | N/A                 | No Pad present                                         |                                                                                                                  |

| <b>A8</b>  | N/A                 | No Pad present                                         |                                                                                                                  |

| B8         | N/A                 | No Pad present                                         |                                                                                                                  |

| C8         | N/A                 | No Pad present                                         |                                                                                                                  |

| D8         | TMN                 | Temperature sense -v common for TMN of all Satellites. |                                                                                                                  |

| E8         | +S                  | Remote sense +v                                        |                                                                                                                  |

| F8         | -S                  | Remote sense -v                                        |                                                                                                                  |

| G8         | SADDR               | Power Management Bus address setting                   | No internal pull-up/pull-down, need outside Resistor. Address setting please Refer to http://www.powerstamp.org/ |

| Н8         | SCL                 | Power Management Bus clock                             | TBC                                                                                                              |

| J8         | SVCLK / AVSCLK      | SVID clock / AVS clock                                 | TBC                                                                                                              |

| К8         | SVALRT /<br>AVSSDAT | SVID alert / AVS SData                                 | TBC                                                                                                              |

| L8         | PAD_ALERT#          | SVI Pad Alert #                                        |                                                                                                                  |

| M8         | N/A                 | No Pad present                                         |                                                                                                                  |

| N8         | N/A                 | No Pad present                                         |                                                                                                                  |

| P8         | N/A                 | No Pad present                                         |                                                                                                                  |

| R8         | N/A                 | No Pad present                                         |                                                                                                                  |

For the description of large pads numbered from 1A1 to 2D5, please refer to the table in: Pin Description – SATELLIT

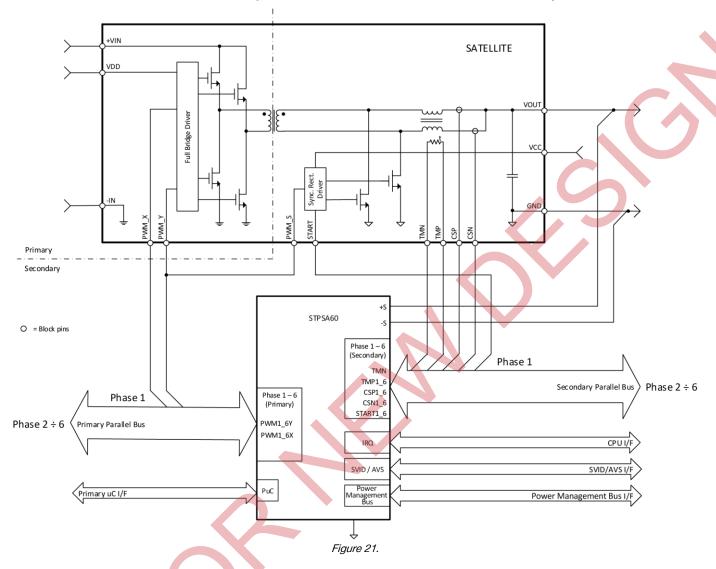

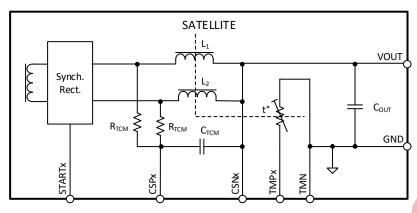

# 19. BLOCK DIAGRAM - SATELLITE (WITH EXTERNAL STPSA60 CONTROLLER)

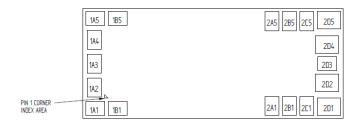

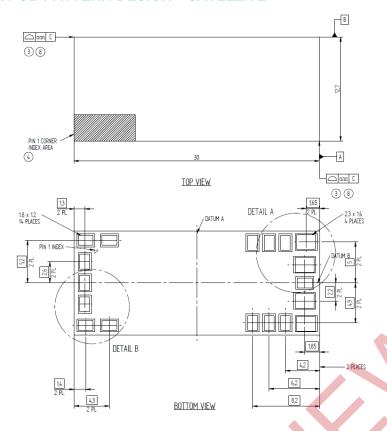

## 20. PACKAGE PINOUT - SATELLITE

TOP VIEW THROUGH THE PRODUCT

| OUTPUT |          |  |  |  |

|--------|----------|--|--|--|

| PIN #  | FUNCTION |  |  |  |

| 2A1    | START    |  |  |  |

| 2A5    | PWM_S    |  |  |  |

| 2B1    | TMN      |  |  |  |

| 2B5    | VCC      |  |  |  |

| 201    | TMP      |  |  |  |

| 205    | CSP      |  |  |  |